# THE 7TH IEEE INTERNATIONAL TEST CONFERENCE IN ASIA (ITC-ASIA) 2023 Kunibiki Messe, Matsue, Shimane, Japan September 12–14, 2023

# **Table of Contents**

| i dieword                                  |

|--------------------------------------------|

| Conference Committees · · · · · 3          |

| General Information · · · · · 6            |

| Venue Floor Plan · · · · · · 7             |

| Exhibition & Poster · · · · · 8            |

| Social Program: Banquet · · · · 9          |

| Overall Agenda · · · · · 10                |

| Tutorials · · · · · 11                     |

| Keynotes · · · · · · 14                    |

| Invited Talks · · · · · 17                 |

| Technical Sessions (Sept. 13) · · · · · 20 |

| Technical Sessions (Sept. 14) · · · · · 23 |

### **Foreword**

Welcome to the 7th International Test Conference in Asia (ITC-Asia 2023)!

International Test Conference (ITC) organized by IEEE has long been the world's premier conference dedicated to the electronic testing technologies - covering the complete cycle from design, verification, manufacturing, test and diagnosis, reliability, and failure analysis. In order to lead the electronic testing community in Asia, ITC-Asia was launched for the first time in Taipei in 2017.

This year the 7th ITC-Asia will be held in Matsue, Shimane prefecture in Japan, on Sept. 12–14 with discussion and interaction between the academia and the industry around the globe. Through attractive sessions on the state-of-the-art test technology trend and the industry topics, attendee can confront challenges faced by the industry, and learn how these challenges are being addressed by the combined efforts of academia, tool and equipment suppliers, designers, and test engineers.

ITC-Asia 2023 received 31 research paper submissions from nine countries and regions. Each paper was sent to at least three reviewers for evaluation, and 13 regular papers and seven short papers were selected based on the reviewers' rating and comments. The selected papers were allocated into seven technical sessions. In addition to the technical sessions, we have further enriched the contents of the conference with the arrangement of two half-day tutorials, two keynote speeches, two invited talks, two 3D chiplet test sessions, three special/industry sessions, five industrial exhibitions, and several high-school student presentations. We would like to thank the Organizing Committee and the Program Committee of ITC-Asia 2023 for their delight hard work in managing all aspects of the conference. Our heartfelt thanks to the ITC-Asia Steering Committee for help for their cooperation.

Finally, we would like to thank our speakers and organizers for their significant contributions to ITC-Asia 2023 and thank the program participants to make the conference successful. We hope that all participants enjoy the conference and the technical discussions.

Hideyuki ICHIHARA

General Co-Chair

Hiroshima City University

Masayuki ARAI

Program Co-Chair

Nihon University

Masahiro ISHIDA

General Co-Chair

ADVANTEST CORPORATION

Satoshi KOMATSU

Program Co-Chair

Tokyo Denki University

### **Organizing Committee**

### **General Co-Chairs**

- Hideyuki ICHIHARA (Hiroshima City University)

- ❖ Masahiro ISHIDA (ADVANTEST CORPORATION)

### **Program Co-Chairs**

- Masayuki ARAI (Nihon University)

- Satoshi KOMATSU (Tokyo Denki University)

#### **Finance Chair**

Senling WANG (Ehime University)

### **Local Arrangement Chair**

Kohei MIYASE (Kyushu Institute of Technology)

### **Industry Co-Chairs**

- Xiaoqing WEN (Kyushu Institute of Technology)

- Shuichi KAMEYAMA (Ehime University)

#### **Tutorial Chair**

Michihiro SHINTANI (Kyoto Institute of Technology)

### **Registration Chair**

Haruhiko KANEKO (Tokyo Institute of Technology)

#### **Publication Chair**

Masayoshi YOSHIMURA (Kyoto Sangyo University)

#### **Publicity Chair**

Tsuyoshi IWAGAKI (Hiroshima City University)

#### **D2T Symposium Liaison**

Akio HIGO (University of Tokyo)

#### **China Liaison**

Huawei LI (Chinese Academy of Sciences)

#### **Taiwan Liaison**

Shi-Yu HUANG (National Tsing Hua University)

#### **Europe Liaison**

Erik LARSSON (Lund University)

### **Steering Committee**

### Chair

Xiaowei LI (Chinese Academy of Sciences)

### Members

- ❖ Tomoo INOUE (Hiroshima City University)

- ❖ Kuen-Jong LEE (National Cheng-Kung University)

- ❖ Li-C. WANG (University of California, Santa Barbara)

- Cheng-Wen WU (National Tsing Hua University)

- Yervant ZORIAN (Synopsys, Inc.)

### **Program Committee**

- John Carulli (GlobalFoundries)

- Mango Chao

(National Yang Ming Chiao Tung University)

- Ching-Hwa Cheng (Feng-Chia University)

- Stephan Eggersglüß (Siemens EDA)

- ❖ Anne Gattiker (IBM)

- Dimitris Gizopoulos (University of Athens)

- Sybille Hellebrand (University of Paderborn)

- Hao-Chiao Hong (National Yang Ming Chiao Tung University)

- Tong-Yu Hsieh (National Sun Yat-sen University)

- Chih-Tsun Huang (National Tsing Hua University)

- Shi-Yu Huang (National Tsing Hua University)

- Jiun-Lang Huang (National Taiwan University)

- Tsung-Chu Huang (National Changhua University of Education)

- Hideyuki Ichihara (Hiroshima City University)

- Michiko Inoue (Nara Institute of Science and Technology)

- Tomoo Inoue (Hiroshima City University)

- Masahiro Ishida (ADVANTEST CORPORATION)

- Tsuyoshi Iwagaki (Hiroshima City University)

- Shuichi Kameyama (Ehime University)

- Haruhiko Kaneko (Tokyo Institute of Technology)

- Saqib Khursheed (University of Liverpool)

- Haruo Kobayashi (Gunma University)

- Amit Kumar

(Cadence Design Systems)

- Soumya Mittal (Qualcomm)

- Jin-Fu Li (National Central University)

- Shu-Min Li (National Sun Yat-sen University)

- Xiaowei Li (Chinese Academy of Sciences)

- Jing-Jia Liou (National Tsing Hua University)

- Erik Jan Marinissen (imec)

- Kohei Miyase (Kyushu Institute of Technology)

- Dimitris Nikolos (University of Patras)

- Alex Orailoglu (University of California, San Diego)

- Rubin Parekhji (Texas Instruments)

- V. Prasanth (Texas Instruments)

- Srivaths Ravi (Texas Instruments)

- Matteo Sonza Reorda (Politecnico di Torino)

- Michihiro Shintani (Kyoto Institute of Technology)

- Hiroshi Takahashi

(Ehime University)

- Kar-Meng Thong

- (Infineon Technologies)◆ Daniel Tille(Infineon Technologies)

- Jerzy Tyszer (Poznan University of Technology)

- Senling Wang (Ehime University)

- Sying-Jyan Wang (National Chung Hsing University)

- Charles H.-P. Wen (National Yang Ming Chiao Tung University)

- Xiaoqing Wen (Kyushu Institute of Technology)

- Dong Xiang (Tsinghua University)

- Masayoshi Yoshimura (Kyoto Sangyo University)

### **General Information**

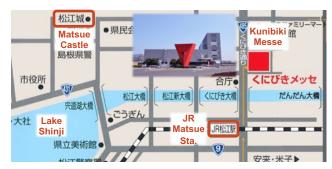

### Venue Location

Kunibiki Messe (Shimane Prefectural Convention Center)

#### **Conference Date**

Day 1: 9:00 am - 4:00 pm, Sept. 12, Tuesday, 2023

Day 2: 8:40 am – 9:00 pm, Sept. 13, Wednesday, 2023

Day 3: 9:00 am - 4:00 pm, Sept. 14, Thursday, 2023

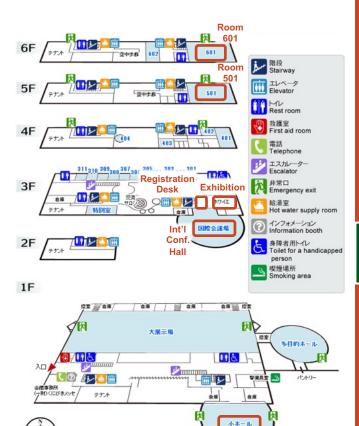

### **Registration Desk**

The registration desk will be located in front of the International Conference Hall on the 3rd floor of Kunibiki Messe. It will be open during the following hours:

Sept. 12, Tue. 8:30 am – 6:00 pm

Sept. 13, Wed. 8:10 am - 4:00 pm

Sept. 14, Thu. 8:30 am – 4:00 pm

Please print your name tag (emailed to you) before you come to the registration desk.

#### Lunch

Lunch will be provided to all attendees on Sept. 13 and Sept. 14. The place for lunch/coffee break is located at the Small Hall in the 1st floor (ground floor) of Kunibiki Messe.

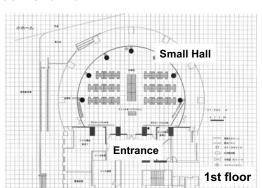

### **Venue Floor Plan**

- Int'l Conf. Hall (3rd floor):

Tutorials, Opening, Keynotes, Invited Talks,

Sessions 1A, 2A, 3A and 4A

(Registration Desk / Industry Exhibition in front of the hall)

- Room 501 (5th floor): Sessions 1B, 2B, 3B and 4B

Small Hall

- ◆ Room 601 (6th floor): Sessions 1C, 2C, 3C and 4C

- ◆ Small Hall (1st floor): Coffee/Lunch Break, Poster Presentations

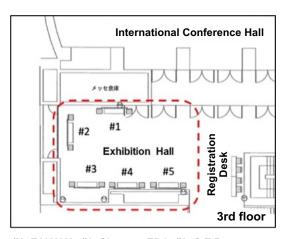

### **Exhibition & Poster**

### **Industry Exhibition**

Period: Sept. 13, Wed., 8:00 am - Sept. 14, Thu., 3:00 pm

Location: Exhibition Hall in front of Int'l Conf. Hall

#1: TAKAYA, #2: Siemens EDA, #3: S.E.R.,

#4: Cadence, #5: FormFactor

#### **Exhibitors:**

- ◆ Cadence Design Systems, Inc. (#4)

- ◆ FormFactor Inc. (#5)

- ◆ S.E.R Corporation (#3)

- ◆ Siemens EDA (#2)

- ◆ TAKAYA Corporation (#1)

#### summaries

### Poster Presentations by High School Students

**Period:** Sept. 14, Thu., 11:00 am – 1:00 pm

Location: Small Hall

### **Social Program: Banquet**

Our banquet will be held at Restaurant "紅葉(Momiji, Red Leaves)" of Yuushien Garden, where you can enjoy a traditional Japanese-style garden, on Sept. 13, from 6:30 pm to 9:00 pm. During the banquet, you can also enjoy Yasugibushi, which is a famous folk song in the Yasugi region, Shimane Prefecture.

The conference registration fee for IEEE Member and Non-member includes a banquet fee. You will find a banquet ticket in your name holder.

Our charter bus transferring from the conference venue to Yuushien and back to the JR Matsue Station is organized. The bus will depart from the conference venue to Yuushien at 5:30 pm, and back to the station at 9:00 pm.

We hope you enjoy our social program!

### Yuushien Garden

### <u>Yasugibushi</u>

# Overall Agenda

|                    |                                                                                           | Int'l Conf. Hall                                                                                                                                                | Room 501                                                                                                                                                                                                                                                                                    | Room 601                                                                                                                                                                                                                                                                                                                                        | ]                                                                                                 |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

|                    | 9:00 am                                                                                   | T Contable biomeric                                                                                                                                             |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

| Sept.12            | 12:00 pm                                                                                  | Scalable hierarchica<br>Lee Harr                                                                                                                                |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

| (Tue.)             | 1:00 pm                                                                                   | Т                                                                                                                                                               |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

| ` '                | -                                                                                         | Silicon Lifecycle Ma                                                                                                                                            |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    | 4:00 pm                                                                                   | Yell Conf. Holl                                                                                                                                                 |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    |                                                                                           | Int'l Conf. Hall                                                                                                                                                | Room 501                                                                                                                                                                                                                                                                                    | Room 601                                                                                                                                                                                                                                                                                                                                        |                                                                                                   |  |  |  |

|                    |                                                                                           |                                                                                                                                                                 | Opening @Int'l Conf. H                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    | 8:40 am                                                                                   |                                                                                                                                                                 | Keynote 1 @Int'l Conf. Hall Semiconductor Packaging Revolution in the Era of Chiplets                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    | 10:50 am                                                                                  |                                                                                                                                                                 | nitsu Orii (Rapidus Corp                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    | 10.50 am                                                                                  | Inv                                                                                                                                                             | ited Talk 1 @Int'l Con<br>Moore Meets Murphy                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    |                                                                                           |                                                                                                                                                                 | Erik Jan Marinissen (im                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    | 10:50 am                                                                                  |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 | Industry Exhibition<br>@Exhibition Hall in                                                        |  |  |  |

|                    | 4-00                                                                                      |                                                                                                                                                                 | Lunch Break @Small H                                                                                                                                                                                                                                                                        | lali                                                                                                                                                                                                                                                                                                                                            |                                                                                                   |  |  |  |

| and the second     | 1:00 pm                                                                                   |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 | front of Int'l Conf. Hall                                                                         |  |  |  |

| Sept. 13           | 1:00 pm                                                                                   | Regular 1A:                                                                                                                                                     | Special 1B:                                                                                                                                                                                                                                                                                 | Special 1C:<br>Siemens Session                                                                                                                                                                                                                                                                                                                  | (flexibly opened during<br>8:00 am – 4:00 pm)                                                     |  |  |  |

| (Wed.)             | 2:15 pm                                                                                   | Hardware Security                                                                                                                                               | 3D Chiplet Test<br>Session 1                                                                                                                                                                                                                                                                | (Silicon Lifecycle                                                                                                                                                                                                                                                                                                                              | 0.00 am = 4.00 pm;                                                                                |  |  |  |

| 3                  | 2.10 piii                                                                                 |                                                                                                                                                                 | 3633011 1                                                                                                                                                                                                                                                                                   | Management)                                                                                                                                                                                                                                                                                                                                     |                                                                                                   |  |  |  |

|                    | 2:15 pm                                                                                   |                                                                                                                                                                 | Coffee Break @Small H                                                                                                                                                                                                                                                                       | lati                                                                                                                                                                                                                                                                                                                                            |                                                                                                   |  |  |  |

|                    | 2:45 pm                                                                                   |                                                                                                                                                                 | onee break @Smail h                                                                                                                                                                                                                                                                         | iaii                                                                                                                                                                                                                                                                                                                                            |                                                                                                   |  |  |  |

|                    | 2:45 pm                                                                                   | D                                                                                                                                                               | Special 2B:                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                               |                                                                                                   |  |  |  |

|                    | -                                                                                         | Regular 2A:<br>Defect Analysis                                                                                                                                  | 3D Chiplet Test                                                                                                                                                                                                                                                                             | Special 2C:<br>Industry Session 1                                                                                                                                                                                                                                                                                                               |                                                                                                   |  |  |  |

|                    | 4:00 pm                                                                                   |                                                                                                                                                                 | Session 2                                                                                                                                                                                                                                                                                   | ,                                                                                                                                                                                                                                                                                                                                               |                                                                                                   |  |  |  |

|                    | 5:30 pm                                                                                   | :                                                                                                                                                               |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    | 9:00 pm                                                                                   |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    | p                                                                                         |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |  |  |  |

|                    |                                                                                           | Int'l Conf. Hall                                                                                                                                                | Room 501                                                                                                                                                                                                                                                                                    | Room 601                                                                                                                                                                                                                                                                                                                                        |                                                                                                   |  |  |  |

|                    |                                                                                           | к                                                                                                                                                               | eynote 2 @Int'l Conf.                                                                                                                                                                                                                                                                       | Hall                                                                                                                                                                                                                                                                                                                                            |                                                                                                   |  |  |  |

|                    |                                                                                           | K<br>Techno                                                                                                                                                     | eynote 2 @Int'l Conf.<br>logy for The Future of C                                                                                                                                                                                                                                           | Hall<br>Computing                                                                                                                                                                                                                                                                                                                               |                                                                                                   |  |  |  |

|                    | 9:00 am                                                                                   | K<br>Techno<br>Shinta                                                                                                                                           | eynote 2 @Int'l Conf.<br>logy for The Future of C<br>ro Yamamichi (IBM Jap                                                                                                                                                                                                                  | Hall<br>Computing<br>an, Ltd.)                                                                                                                                                                                                                                                                                                                  |                                                                                                   |  |  |  |

|                    |                                                                                           | Techno<br>Shinta<br>Invi<br>Test Industry Challen                                                                                                               | eynote 2 @Int'l Conf.<br>logy for The Future of C<br>ro Yamamichi (IBM Jap<br>ited Talk 2 @Int'l Conf<br>ges and Solutions as O                                                                                                                                                             | Hall Computing ean, Ltd.)  f. Hall bserved by the Leading                                                                                                                                                                                                                                                                                       |                                                                                                   |  |  |  |

|                    | 9:00 am                                                                                   | K Techno Shinta Inv Test Industry Challen Physical                                                                                                              | eynote 2 @Int'l Conf.<br>logy for The Future of C<br>ro Yamamichi (IBM Jap<br>ited Talk 2 @Int'l Conf<br>ges and Solutions as O<br>Implementation Solutio                                                                                                                                   | Hall Computing an, Ltd.)  f. Hall bserved by the Leading on Provider                                                                                                                                                                                                                                                                            |                                                                                                   |  |  |  |

|                    | 9:00 am<br>_<br>10:50 am                                                                  | K Techno Shinta Inv Test Industry Challen Physical                                                                                                              | eynote 2 @Int'l Conf.<br>logy for The Future of C<br>ro Yamamichi (IBM Jap<br>ited Talk 2 @Int'l Conf<br>ges and Solutions as O                                                                                                                                                             | Hall Computing an, Ltd.)  f. Hall bserved by the Leading on Provider                                                                                                                                                                                                                                                                            |                                                                                                   |  |  |  |

|                    | 9:00 am                                                                                   | K<br>Techno<br>Shinta<br>Inv<br>Test Industry Challen<br>Physical<br>Janet Ols                                                                                  | eynote 2 @Int'l Conf.<br>logy for The Future of C<br>ro Yamamichi (IBM Jap<br>ited Talk 2 @Int'l Coni<br>ges and Solutions as O<br>Implementation Solution<br>(Cadence Design S)                                                                                                            | Hall Demputing an, Ltd.)  f. Hall bserved by the Leading in Provider systems, Inc.)                                                                                                                                                                                                                                                             | Industry Exhibition @Exhibition Hall in                                                           |  |  |  |

| Sept. 14           | 9:00 am<br>_<br>10:50 am                                                                  | K<br>Techno<br>Shinta<br>Inv<br>Test Industry Challen<br>Physical<br>Janet Ols                                                                                  | eynote 2 @Int'l Conf.<br>logy for The Future of C<br>ro Yamamichi (IBM Jap<br>ited Talk 2 @Int'l Con<br>ges and Solutions as O<br>Implementation Solutio<br>on (Cadence Design S)                                                                                                           | Hall Demputing an, Ltd.)  f. Hall bserved by the Leading in Provider systems, Inc.)                                                                                                                                                                                                                                                             | @Exhibition Hall in<br>front of Int'l Conf. Hall                                                  |  |  |  |

| Sept. 14<br>(Thu.) | 9:00 am<br>                                                                               | K Techno Shinta Inv Test Industry Challen Physical Janet Ols  Lunch Break / Posi  Regular 3A:                                                                   | eynote 2 @Int'l Conf.<br>logy for The Future of C<br>ro Yamamichi (IBM Jap<br>ited Talk 2 @Int'l Coni<br>ges and Solutions as O<br>Implementation Solution<br>(Cadence Design S)                                                                                                            | Hall Demputing an, Ltd.)  f. Hall bserved by the Leading in Provider systems, Inc.)                                                                                                                                                                                                                                                             | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during                       |  |  |  |

|                    | 9:00 am<br>10:50 am<br>10:50 am<br>1:00 pm                                                | K Techno Shinta Inv Test industry Challen Physical Janet Ols  Lunch Break / Post  Regular 3A: Processor/Software                                                | eynote 2 @Int'l Conf. logy for The Future of C ro Yamamichi (IBM Jap tted Talk 2 @Int'l Conf ges and Solutions as O Implementation Solutio on (Cadence Design S) ter Presentations by h @Small Hall                                                                                         | Hall Computing an, Ltd.) f. Hall bserved by the Leading on Provider rstems, Inc.) ligh School Students                                                                                                                                                                                                                                          | @Exhibition Hall in<br>front of Int'l Conf. Hall                                                  |  |  |  |

|                    | 9:00 am<br>10:50 am<br>10:50 am<br>1:00 pm<br>1:00 pm<br>2:15 pm                          | K Techno Shinta Inv Test Industry Challen Physical Janet Ols  Lunch Break / Posi  Regular 3A:                                                                   | eynote 2 @Int'l Conf. ogy for The Future of C r Yamamichi (IBM Jap ted Talk 2 @Int'l Con ges and Solutions as O implementation Solutio on (Cadence Design S) er Presentations by h @Small Hall  Regular 3B:                                                                                 | Hall Computing an, Ltd.)  f. Hall bserved by the Leading on Provider stems, Inc.)  ligh School Students  Special 3C:                                                                                                                                                                                                                            | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during                       |  |  |  |

|                    | 9:00 am<br>10:50 am<br>10:50 am<br>1:00 pm<br>1:00 pm<br>2:15 pm<br>2:15 pm               | K Technon Shinta Inv Test Industry Challen Physical Janet Ols Lunch Break / Post Regular 3A: Processor/Software Testing                                         | eynote 2 @Int'l Conf. ogy for The Future of C r Yamamichi (IBM Jap ted Talk 2 @Int'l Con ges and Solutions as O implementation Solutio on (Cadence Design S) er Presentations by h @Small Hall  Regular 3B:                                                                                 | Hall Computing an, Ltd.)  f. Hall bserved by the Leading in Provider stems, inc.)  ligh School Students  Special 3C: Industry Session 2                                                                                                                                                                                                         | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during                       |  |  |  |

|                    | 9:00 am<br>10:50 am<br>10:50 am<br>1:00 pm<br>1:00 pm<br>2:15 pm<br>2:15 pm<br>2:45 pm    | K Techno Shinta Inv Test Industry Challen Physical Janet Ols  Lunch Break / Post  Regular 3A: Processor/Software Testing                                        | eynote 2 @Int'l Conf. ogy for The Future of C oy Yamamichi (IBM Jap ted Talk 2 @Int'l Con ges and Solutions as O Implementation Solution on (Cadence Design S) er Presentations by H @Small Hall  Regular 3B: Fault Tolerant Latch                                                          | Hall Computing an, Ltd.) f. Hall bserved by the Leading in Provider rstems, Inc.) ligh School Students  Special 3C: Industry Session 2                                                                                                                                                                                                          | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during                       |  |  |  |

|                    | 9:00 am<br>10:50 am<br>10:50 am<br>1:00 pm<br>1:00 pm<br>2:15 pm<br>2:15 pm               | K Technon Shinta Inv Test Industry Challen Physical Janet Ols Lunch Break / Post Regular 3A: Processor/Software Testing                                         | eynote 2 @Int'l Conf. ogy for The Future of C r Yamamich (IBM Jap ted Talk 2 @Int'l Conf ges and Solutions as O Implementation Solution (Cadence Design S) ter Presentations by h @Small Hall  Regular 3B: Fault Tolerant Latch  Coffee Break @Small h  Regular 4B:                         | Hall Computing an, Ltd.)  f. Hall bserved by the Leading in Provider ristems, Inc.)  ligh School Students  Special 3C: Industry Session 2                                                                                                                                                                                                       | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during                       |  |  |  |

|                    | 9:00 am<br>10:50 am<br>10:50 am<br>1:00 pm<br>1:00 pm<br>2:15 pm<br>2:15 pm<br>2:45 pm    | K Techno Shinta Inv Test Industry Challen Physical Janet Ols  Lunch Break / Post  Regular 3A: Processor/Software Testing                                        | eynote 2 @Int'l Conf. ogy for The Future of C or Yamamichi (IBM Jap ted Talk 2 @Int'l Con ges and Solutions as O Implementation Solution on (Cadence Design S) ter Presentations by h @Small Hall  Regular 3B: Fault Tolerant Latch                                                         | Hall Computing an, Ltd.) f. Hall bserved by the Leading in Provider rstems, Inc.) ligh School Students  Special 3C: Industry Session 2                                                                                                                                                                                                          | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during                       |  |  |  |

|                    | 9:00 am<br>10:50 am<br>10:50 am<br>1:00 pm<br>1:00 pm<br>2:15 pm<br>2:45 pm<br>2:45 pm    | K Technon Shinta Inv Test Industry Challen Physical Janet Ols Lunch Break / Post Regular 3A: Processor/Software Testing                                         | eynote 2 @Int'l Conf. ogy for The Future of C r Yamamich (IBM Jap ted Talk 2 @Int'l Conf ges and Solutions as O Implementation Solution (Cadence Design S) ter Presentations by h @Small Hall  Regular 3B: Fault Tolerant Latch  Coffee Break @Small h  Regular 4B:                         | Hall Computing an, Ltd.)  f. Hall bserved by the Leading in Provider strems, Inc.)  ligh School Students  Special 3C: Industry Session 2  lall  Regular 4C: Jitter and Error                                                                                                                                                                    | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during                       |  |  |  |

|                    | 9:00 am<br>10:50 am<br>10:50 am<br>1:00 pm<br>1:00 pm<br>2:15 pm<br>2:45 pm<br>2:45 pm    | K Technon Shinta Inv Test Industry Challen Physical Janet Ols Lunch Break / Post Regular 3A: Processor/Software Testing                                         | eynote 2 @Int'l Conf. ogy for The Future of C r Yamamich (IBM Jap ted Talk 2 @Int'l Conf ges and Solutions as O Implementation Solution (Cadence Design S) ter Presentations by h @Small Hall  Regular 3B: Fault Tolerant Latch  Coffee Break @Small h  Regular 4B:                         | Hall Computing an, Ltd.)  f. Hall bserved by the Leading in Provider strems, Inc.)  ligh School Students  Special 3C: Industry Session 2  lall  Regular 4C: Jitter and Error                                                                                                                                                                    | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during                       |  |  |  |

| (Thu.)             | 9:00 am<br>10:50 am<br>10:50 am<br>1:00 pm<br>1:00 pm<br>2:15 pm<br>2:45 pm<br>2:45 pm    | K Technon Shinta Inv Test Industry Challen Physical Janet Ols  Lunch Break / Post  Regular 3A: Processor/Software Testing  Regular 4A: Testing and Verification | eynote 2 @Int'l Conf. logy for The Future of C or Yamamichi (IBM Jap ted Talk 2 @Int'l Con ges and Solutions as O Implementation Solutio on (Cadence Design S) er Presentations by h @Small Hall  Regular 3B: Fault Tolerant Latch  Coffee Break @Small H  Regular 4B: Memory               | Hall Computing an, Ltd.)  f. Hall bserved by the Leading in Provider strems, Inc.)  ligh School Students  Special 3C: Industry Session 2  lall  Regular 4C: Jitter and Error                                                                                                                                                                    | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during<br>8:00 am – 3:00 pm) |  |  |  |

| (Thu.)             | 9:00 am 10:50 am 10:50 am 1:00 pm 1:00 pm 2:15 pm 2:15 pm 2:45 pm 4:00 pm                 | K Techno Shinta Inv Test Industry Challen Physical Janet Ols  Lunch Break / Post Regular 3A: Processor/Software Testing  Regular 4A: Testing and Verification   | eynote 2 @int'l Conf. ogy for The Future of C r Yamamich (IBM Jap ted Talk 2 @int'l Conf. ges and Solutions as O implementation Solution on (Cadence Design S) ter Presentations by h @Small Hall  Regular 3B: Fault Tolerant Latch Coffee Break @Small h Regular 4B: Memory  : Opening, Ke | Hall Computing an, Ltd.)  f. Hall bserved by the Leading in Provider stems, Inc.)  ligh School Students  Special 3C: Industry Session 2  Industry Session 2 | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during<br>8:00 am – 3:00 pm) |  |  |  |

| (Thu.)             | 9:00 am 10:50 am 10:50 am 1:00 pm 1:00 pm 2:15 pm 2:15 pm 2:45 pm 4:00 pm                 | K Technon Shinta Inv Test Industry Challen Physical Janet Ols  Lunch Break / Post  Regular 3A: Processor/Software Testing  Regular 4A: Testing and Verification | eynote 2 @Int'l Conf. logy for The Future of C or Yamamichi (IBM Jap ted Talk 2 @Int'l Con ges and Solutions as O Implementation Solutio on (Cadence Design S) er Presentations by h @Small Hall  Regular 3B: Fault Tolerant Latch  Coffee Break @Small H  Regular 4B: Memory               | Hall Computing an, Ltd.)  f. Hall bserved by the Leading in Provider stems, Inc.)  ligh School Students  Special 3C: Industry Session 2  Industry Session 2 | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during<br>8:00 am – 3:00 pm) |  |  |  |

| (Thu.)             | 9:00 am 10:50 am 10:50 am 1:00 pm 1:00 pm 2:15 pm 2:15 pm 2:45 pm 2:45 pm 3:45 pm 4:00 pm | K Technon Shinita Inv Test Industry Challen Physical Janet Ols Lunch Break / Post Regular 3A: Processor/Software Testing  Regular 4A: Testing and Verification  | eynote 2 @Int'l Conf. logy for The Future of C or Yamamichi (IBM Jap ted Talk 2 @Int'l Con ges and Solutions as O Implementation Solutio no (Cadence Design S) er Presentations by h @Small Hall  Regular 3B: Fault Tolerant Latch  Coffee Break @Small h Regular 4B: Memory  : Opening, Ke | Hall Computing an, Ltd.)  f. Hall bserved by the Leading in Provider rstems, Inc.)  ligh School Students  Special 3C: Industry Session 2  Itall  Regular 4C: Jitter and Error Mitigation  eynotes, Invited Tale                                                                                                                                 | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during<br>8:00 am – 3:00 pm) |  |  |  |

| (Thu.)             | 9:00 am 10:50 am 10:50 am 1:00 pm 1:00 pm 2:15 pm 2:15 pm 2:45 pm 4:00 pm                 | K Technon Shinita Inv Test Industry Challen Physical Janet Ols Lunch Break / Post Regular 3A: Processor/Software Testing  Regular 4A: Testing and Verification  | eynote 2 @Int'l Conf. logy for The Future of C or Yamamichi (IBM Jap ted Talk 2 @Int'l Con ges and Solutions as O Implementation Solutio no (Cadence Design S) er Presentations by h @Small Hall  Regular 3B: Fault Tolerant Latch  Coffee Break @Small h Regular 4B: Memory  : Opening, Ke | Hall Computing an, Ltd.)  f. Hall bserved by the Leading in Provider stems, Inc.)  ligh School Students  Special 3C: Industry Session 2  Industry Session 2 | @Exhibition Hall in<br>front of Int'l Conf. Hall<br>(flexibly opened during<br>8:00 am – 3:00 pm) |  |  |  |

### **Tutorials**

### **Tutorial 1**

9:00 am - 12:00 pm, Sept. 12 Tue., @Int'l Conf. Hall

Scalable hierarchical DFT technologies for AI, SOC and multi-die

Lee Harrison and Wu Yang (Siemens EDA)

#### Abstract:

In this tutorial, we will proceed to give an overview of the exciting field of AI and HPC. It will cover the critical and special characteristics and the architecture of the popular AI chips. Next, we will summarize the features of the Al chips from design-for-test (DFT) perspective and introduce the DFT technologies that can help testing Al chips. Similarly, we will the discussion on DFT for typical HPC SOC designs. We will also look at how the shift to 2.5D and 3D including Chiplet development is changing the industry, the new challenges added for the DFT community and the solutions. Finally, we will present a few case studies on how DFT is implemented in the real Al chips. We will also present some of the functional monitoring techniques that are available today. An overall architecture showing how functional monitoring can be implemented and how the monitor data can be used to manage in-life capabilities.

#### About the Lecturers:

Lee Harrison, is Tessent Product Marketing Director for safety and security, at Siemens EDA. He has over 20 years of industry experience with Siemens Tessent test, safety and security products, with a focus on automotive, Lee is working to ensure that current and future test, safety, security and analytics requirements of Siemens's automotive customers

are understood and met. Lee received his BEng in Micro Electronic Engineering from Brunel University London in 1996.

Wu Yang is the Director of marketing at Siemens EDA. With more than 24 years of experiences in DFT, 3D IC, silicon learning and testing, Mr. Yang has been a frequent speaker at many conferences and a regular contributor to papers and articles. He delivered multiple tutorials at ITC, ATS, ETS and VTS. Mr. Yang received a MS degree in electrical engineering

from Portland State University.

### **Tutorials**

#### **Tutorial 2**

1:00 pm – 4:00 pm, Sept. 12 Tue., @Int'l Conf. Hall

Silicon Lifecycle Management: Trends, Challenges and Solutions

Yervant Zorian (Synopsys, Inc.)

#### Abstract:

Recent advances in automotive SOCs, artificial intelligence accelerators, and high-performance computing engines in data centers have led to an explosion in the adoption of emerging technology nodes and 3DIC/chiplet packages. This tutorial will present today's trends and discuss on the resiliency challenges for such emerging SOCs. It will then focus on optimizing the SOC health using advanced solutions typically utilized for managing the different silicon lifecycle stages: from silicon debug in early bring up stage to shorten the time-to-volume; to self-test and repair during volume production stage, in order to improve quality and yield; to power-on self-test in the field stage to address aging challenges; to periodic checking in-system to improve functional safety; and finally to fault tolerance and error correction during mission mode to address a range of transient errors. All of the above optimizations materialized by on-chip and/or off-chip data analytics.

#### About the Lecturer:

Dr. Yervant Zorian is a Chief Architect and Fellow at Synopsys, as well as President of Synopsys Armenia. Formerly, he was Vice President and Chief Scientist of Virage Logic, Chief Technologist at LogicVision, and a Distinguished Member of Technical Staff AT&T Bell Laboratories. He is currently the President of IEEE Test Technology Technical Council

(TTTC), the founder and chair of the IEEE 1500 Standardization Working Group, the Editor-in-Chief Emeritus of the IEEE Design and Test of Computers and an Adjunct Professor at University of British Columbia. He served on the Board of Governors of Computer Society and CEDA, was the Vice President of IEEE Computer Society, and the General Chair of the 50th Design Automation Conference (DAC) and several other symposia and workshops.

### **Tutorials**

Dr. Zorian holds 35 US patents, has authored four books, published over 350 refereed papers and received numerous best paper awards. A Fellow of the IEEE since 1999, Dr. Zorian was the 2005 recipient of the prestigious Industrial Pioneer Award for his contribution to BIST, and the 2006 recipient of the IEEE Hans Karlsson Award for diplomacy. He received the IEEE Distinguished Services Award for leading the TTTC, the IEEE Meritorious Award for outstanding contributions to EDA, and in 2014, the Republic of Armenia's National Medal of Science.

He received an MS degree in Computer Engineering from University of Southern California, a PhD in Electrical Engineering from McGill University, and an MBA from Wharton School of Business, University of Pennsylvania.

### **Keynotes**

### Keynote 1

9:00 am – 9:50 am, Sept. 13 Wed., @Int'l Conf. Hall

Chair: Masahiro Ishida (ADVANTEST CORPORATION)

### Semiconductor Packaging Revolution in the Era of Chiplets

Yasumitsu Orii (Rapidus Corporation)

#### Abstract:

Since the semiconductor cost for state-of-the-art nodes is increasing, "Chiplet" technology is in the spotlight as a new evolutionary path to scale up integration and improve performance and reduce the total cost. With an SoC, a chip might incorporate a CPU, plus an additional several IP blocks on the same chip. That design is then scaled by the advanced node, which is an expensive process. With a chiplet model, those several IP blocks are hardened into smaller dies(chiplets) and those dies are integrated on an interposer to build a system. Those chips must be connected in the shortest length while considering signal integrity and power integrity so that the cutting-edge packaging technology is the key to improve the performance of IT equipments. In this presentation, the advanced 2.1D, 2.3D, 2.5D and 3D packaging technologies will be introduced as well as the several interposer technologies.

### About the Speaker:

Dr. Yasumitsu Orii joined IBM Japan in 1986 and was a leading expert on Flip Chip organic packages, which had contributed to the performance improvements and miniaturization of such products as servers, laptop computers, and HDDs. The packaging technology is becoming more important for next generation server products as Moore's Law reaches its

limits. His flip chip expertise extended into many related areas. Initially, he was a pioneer of flip chip on FPC (Flexible Printed Circuit) for HDDs, which allowed the read/write amplifier ICs to be mounted on the suspension and much closer to the GMR head. Later, he developed the C2 (Chip Connection) technology that supported low-cost 50-µm-pitch flip chip bonding for the commodity consumer electronics market and it was licensed to a company in Taiwan. At IBM Research Tokyo, he was leading the next generation flip chip organic package, 3D-IC projects and Neuromorphic Computing for IBM Servers and creating new technologies under a Joint Development Program involving many leading Japanese materials companies. He left IBM in 2014 and joined NAGASE & CO., LTD.

### **Keynotes**

He established "New Value Creation Office" under the direct control of the president and launched the material informatics software as a service in 2020. He left NAGASE and he joined Rapidus Corporation in 2022/Dec. Now he is the senior managing executive officer to lead the 3D Assembly Division. He is IMAPS(International Microelectronics Assembly and Packaging Society) Fellow, IEEE EPS(Electronics Packaging Society) Senior member.

### **Keynotes**

### **Keynote 2**

9:00 am – 9:50 am, Sept. 14 Thu., @Int'l Conf. Hall

Chair: Hideyuki Ichihara (Hiroshima City University)

### Technology for The Future of Computing

Shintaro Yamamichi (IBM Japan, Ltd.)

#### Abstract:

We are now facing a dramatical transformation in the IT especially computing technologies. generation of the transistors, having a gate-all-around and structure, is developed. parallel, nanosheet In semiconductor chips dedicated for the Al workload have been intensively studied. One technology, called Digital Core, can save the energy by reducing the precision in the calculation. The other technology, called Analog Core, utilizes non-volatile memory elements to represent the weights of the neural network in an analog way, and performs multiply and accumulate operation by mechanism. Since it is quite difficult to implement all these technologies and architectures in one die, the advanced packaging technology, including testing methodology, will play a critical role in terms of system integration. Especially in a small form factor, such as in interposer substrate scale, the "chiplet" platform with both technology and design aspects should be developed, and recognized in the semiconductor ecosystem. Several chiplet technologies, such as micro bumping and Si bridge interconnect, will be introduced.

### About the Speaker:

Shintaro Yamamichi received his M.E. and Ph. D. degrees in electrical engineering, from Kyoto University, Japan in 1989 and 2002, respectively. He was involved in both semiconductor and packaging process research in NEC and Renesas Electronics. He was also a visiting industrial fellow at University of

California, Berkeley in 1997. In 2013, he joined the Science and Technology team in IBM Research -Tokyo. From 2016, He led the research projects, including quantum computer installation, Al hardware, advanced packaging and material informatics. Currently, he is the Director of Semiconductors, IBM Research -Tokyo, leading all the semiconductor-related research and development activities in IBM Japan.

### **Invited Talks**

### **Invited Talk 1**

10:00 am - 10:50 am, Sept. 13 Wed., @Int'l Conf. Hall

Chair: Masayuki Arai (Nihon University)

### Moore Meets Murphy

Erik Jan Marinissen (imec)

### Abstract:

Gordon Moore's iconic 1965 article unwittingly laid the foundation for a remarkably accurate prediction that has withstood the test of time. His forecast has turned into an industry target, holding immense significance. For decades, downsizing metal and poly pitches effortlessly propelled progress, but now the technical and economical limits of this scaling approach are in sight. Today, the semiconductor industry seeks salvation in the vertical dimension through die stacking, commonly referred to as "chiplet-based design". However, even these multi-die packages, like all integrated circuits, are susceptible to Murphy's Law and necessitate rigorous testing for manufacturing defects. Beyond the usual obstacles of test content, accessibility, and cost, chipletbased ICs present their own unique set of test challenges. This presentation aims to scrutinize these hurdles and explore emerging solutions, if available.

### About the Speaker:

Erik Jan Marinissen is Scientific Director at imec in Leuven, Belgium, where he is responsible for research on test and design-for-test, covering topics as diverse as 3D-stacked ICs, silicon photonics, CMOS technology nodes below 10nm, and STT-MRAMs. In addition, he holds the position of Visiting Researcher at Eindhoven University of Technology (TU/e) in the Netherlands.

Previously, he worked at NXP Semiconductors and Philips Research Laboratories in Eindhoven, Nijmegen, and Sunnyvale. He holds an MSc degree in Computing Science (1990) and a PDEng degree in Software Technology (1992) from TU/e. Marinissen has an extensive publication record, co-authoring more than 285 journal and conference papers and being involved in the invention of eighteen US/EP patent families.

### **Invited Talks**

Marinissen has played significant roles in standardization and academic initiatives. He served as Editor-in-Chief of IEEE Std 1500™-2005, which focuses on embedded core test access, and initiated and chaired IEEE Std 1838™-2019, addressing 3D test access. Additionally, he founded workshops such as 'Diagnostic Services in Network-on-Chips', '3D Integration Workshop', and the IEEE 'International Workshop on Testing Three-Dimensional Stacked ICs'. Marinissen has also taken on key positions as Program Chair and General Chair for several conferences. including DDECS, ETS, 3D-TEST, 3DC-TEST, DATE, ETW, DSNOC, and 3DIW. Moreover, he serves on various conference committees, contributing to events such as ATS, DATE, ETS, ITC, ITC-Asia, and VTS. Marinissen serves on the editorial boards of IEEE 'Design & Test' and Springer's 'Journal of Electronic Testing: Theory and Applications'. Throughout his career, Marinissen has received numerous prestigious awards, including Best Paper Awards at various conferences and symposiums. Both in 2008 and 2010, he won the Most Significant Paper Awards at the IEEE International Test Conference (ITC), In 2017, he received both the National Instruments' Engineering Impact Award and the IEEE Standards Association's Emerging Technology Award. At ITC 2021, Marinissen received the TTTC Bob Madge Innovation Award. Notably, he was recognized as the most-cited author of ITC papers from 1995 to 2019 on ITC's 50th anniversary in 2019. He is also included in the list of "Top-2% Scientists World-Wide in All Disciplines" published by Elsevier and Stanford University. Marinissen is a Fellow of IEEE, a Distinguished Contributor Charter Member, and a Golden Core Member of IEEE Computer Society. He served as an elected member of the IEEE Computer Society's Board of Governors from 2019 to 2021. Marinissen has also shared his expertise through tutorials and in-house company courses on Core-Based SOC Test, 3D-SIC Test, and Improving ATPG Test Quality at various international conferences and events.

As an educator, Marinissen has supervised over 49 international MSc and PhD students, fostering their growth and development in the field. Notably, Dan Adolfsson, one of his MSc students from Linköping Universitet in Sweden, received the "Sveriges Ingenjörer 'Lilla Polhempriset'" in 2007 for his outstanding MSc graduation project supervised by Marinissen at NXP Semiconductors. Furthermore, Lizhou Wu, a PhD student at TU Delft in the Netherlands, was honored with the TTTC Edward J. McCluskey Best Doctoral Thesis Award in Test at ITC in 2021 for his exceptional PhD thesis titled "Testing STT-MRAM: Manufacturing Defects, Fault Models, and Test Solutions", which received a "cum laude" distinction.

### **Invited Talks**

#### **Invited Talk 2**

10:00 am – 10:50 am, Sept. 14 Thu., @Int'l Conf. Hall

Chair: Satoshi Komatsu (Tokyo Denki University)

Test Industry Challenges and Solutions as Observed by the Leading Physical Implementation Solution Provider

Janet Olson (Cadence Design Systems, Inc.)

#### Abstract:

Test is a mission critical aspect of the design process, but design functionality/verification consumes the significant majority of engineering focus, with test often retrofitted late in the design cycle. The era of point-tools is over, what's needed is deep collaboration across the flow from state-of-the-art design IP, verification, physical design, and packaging. New solutions must manage test structures from multiple sources and meet coverage, test time, and PPA (power, performance, area) goals without introducing design closure iterations. This presentation offers a new way forward, borne from Cadence's unique perspective gained from experience working with global semiconductor suppliers engineering test into some of the world's most complicated designs.

### About the Speaker:

Janet Olson is Vice President Research and Development for Front-End Design at Cadence Design Systems. Janet is responsible for Modus, Cadence's IC test solution, high level synthesis (Stratus) and constraint verification (Litmus). Janet has a master's degree in Electrical Engineering from Stanford and a bachelor's degree from CMU and holds 7 US patents. Janet has been recognized with the 2017 Marie R. Pistilli Electronic Design Award and the 2016 YWCA Tribute to Women award.

### Sessions (Sept. 13)

Date: Sept. 13, Wednesday

Time: 1:00 pm - 2:15 pm

Suffix 's': short presentation

Regular 1A: Hardware Security

Location: Int'l Conf. Hall

Chair: Jiun-Lang Huang (National Taiwan Univ.)

### [1A-1] A Physically Unclonable Function Using Time-to-Digital Converter with Linearity Self-Calibration and its FPGA Implementation

Kentaroh Katoh (Fukuoka University), Shuhei Yamamoto, Zheming Zhao, Yujie Zhao, Shogo Katayama, Anna Kuwana, Takayuki Nakatani, Kazumi Hatayama, Haruo Kobayashi (Gunma University), Keno Sato, Takashi Ishida, Toshiyuki Okamoto and Tamotsu Ichikawa (ROHM Semiconductor)

# [1A-2] Hunting for Hardware Trojan in Gate Netlist: A Stacking Ensemble Learning Perspective

Liang Hong, Ge Zhu (Northwestern Polytechnical University), Jing Zhou (Beijing Microelectronics Technology Institute), Xuefei Li, Ziyi Chen and Wei Hu (Northwestern Polytechnical University)

### [1A-3s] Optimizing Post-Silicon Validation for FPGA Serial Configuration using an Automation Framework and Timing Characterization Verification

Mohd Amiruddin Zainol, Khamron Sompon and Gua Bin Ng (Intel Corporation)

### Special 1B: 3D Chiplet Test Session 1

Location: Room 501

Chair: Xiaoqing Wen (Kyushu Institute of

Technology)

[1B-1] On-Chip Timing Circuits for Finding Who's Accountable When a 3D Chiplet IC Fails

Shi-Yu Huang (National Tsing Hua University)

[1B-2] Generating Test Patterns for Chiplet Interconnects: Achieving Optimal Effectiveness and Efficiency

Po-Yao Chuang (imec)

### Sessions (Sept. 13)

Special 1C: Siemens Session

(Silicon Lifecycle Management)

Location: Room 601

Chair: Wu Yang (Siemens EDA)

[1C-1] Silent Data Corruption (SDC) Failures — What Do We Know about the Root Causes? Phil Nigh (Broadcom, Inc.)

r riii riigir (Breddeerri, me.)

[1C-2] Production Test Impacts of Chiplet Integration within a 3DIC

Vineet Pancholi (Amkor Technology, Inc.)

[1C-3] Functional Monitoring of Complex Chips Lee Harrison (Siemens EDA)

[1C-4] High Protocol Scan with System Level Test John Jackson (Teradyne, Inc.)

Date: Sept. 13, Wednesday Time: 2:45 pm – 4:00 pm

Suffix 's': short presentation

Regular 2A: Defect Analysis

Location: Int'l Conf. Hall

Chair: Andre Ivanov (The Univ. of British Columbia)

[2A-1] Toward Improvement and Evaluation of Reconstruction Capability of CapsNet-Based Wafer Map Defect Pattern Classifier

Yuki Yamanaka (Tokyo Metropolitan University), Masayuki Arai (Nihon University), Yoshikazu Nagamura and Satoshi Fukumoto (Tokyo Metropolitan University)

[2A-2] Parametric Faults in Computing-in-Memory Applications of a 4kb Read-Decoupled 8T SRAM Array in 40nm CMOS

Hao-Chiao Hong, Chien-Hung Chen and Yu-Wun Chen (National Yang Ming Chiao Tung University)

[2A-3s] Trustworthy Lifetime Prediction by Aging History Analysis and Multi-Level Stress Test Chen-Lin Tsai and Shi-Yu Huang (National Tsing Hua University)

### Sessions (Sept. 13)

Special 2B: 3D Chiplet Test Session 2

Location: Room 501

Chair: Senling Wang (Ehime University)

[2B-1] Emerging Trends, Challenges and Solutions for Probing Next Generation Advanced Packaging Devices