Dec. 16 / 17 / 18 / 19

All rooms (101, 701, 702, and 802) are located in Conference Tower.

*: presenter

Dec. 16 (Tuesday) 9:45 am – 12:00 pm

Tutorial 1 @Room 701

[T1] Designing Chiplets & 3DIC for Silicon Lifecycle Management

*Yervant Zorian (Synopsys)

Dec. 16 (Tuesday) 1:30 pm – 3:40 pm

Tutorial 2 @Room 701

[T2] Enhancing Trustworthiness in the Global IC Supply Chain

*Giorgio Di Natale (Université Grenoble-Alpes)

Dec. 17 (Wednesday) 9:00 am – 11:40 am

Opening / Keynote 1 / Invited Talk 1 @Room 101

Chair: Hideyuki Ichihara (Hiroshima City University)

9:00 am – 10:00 pm:

[Op] Opening

10:00 am – 10:50 am:

[K1] New Design for Test Technologies for the Angstrom Era Multi-Die Designs

*Janusz Rajski (Siemens EDA)

10:50 am – 11:40 am:

[I1] 3DIC and advanced packaging technologies for enabling the evolution of AI

*Ryutaro Yasuhara (TSMC Japan 3DIC R&D Center)

Dec. 17 (Wednesday) 1:00 pm – 2:40 pm

Session 1 (ATS) @Room 101: DFT, BIST and Fault Simulation

Chair: Alex Orailoglu (University of California, San Diego)

1:00 pm – 1:25 pm:

[RS1-1] A Don’t Care Filling Method for Control Signals on State Transitions of Controllers to Minimize the Estimated Number of Test Patterns for Data-Paths

*Haruta Tokuta, Toshinori Hosokawa (Nihon University), Masayoshi Yoshimura (Kyoto Sangyo University), Masayuki Arai (Nihon University)

1:25 pm – 1:50 pm:

[RS1-2] Weight-Aware Scan Chain Stitching for Shift Power Minimization under Routing Constraints

*Rohit Badjatya, Kapil Sharma (Indian Institute of Technology Bombay), Makoto Ikeda, Masahiro Fujita (University of Tokyo), Virendra Singh (Indian Institute of Technology Bombay)

1:50 pm – 2:15 pm:

[RS1-3] Automatic Cell-Aware Software-Based Self-Test Generation for a RISC-V Core Local Interrupt Controller

*Tobias Faller, Bernd Becker (University of Freiburg)

2:15 pm – 2:40 pm:

[RS1-4] Application-Aware Early-Exit Fault Classification for Video Decoder Using Miter-Based Analysis

*Jun-Tsung Wu (Department of Electrical Engineering, National Sun Yat-sen University), Tong-Yu Hsieh (National San Yat-san University)

ATS Doctoral Thesis Award Contest @Room 702

Chair: Satoshi Ohtake (Oita University)

1:20 pm – 1:25 pm:

Opening (ATS Doctoral Thesis Award Contest)

1:25 pm – 1:45 pm:

Securing the Test Infrastructure of SoCs

*Anjum Riaz (Indian Institute of Technology (IIT) Jammu)

1:45 pm – 2:05 pm:

Physical Security of Emerging AI Hardware Accelerators: From Vulnerabilities to Countermeasures

*Brojogopal Sapui (Chair of Dependable Nano Computing (CDNC), Karlsruhe Institute of Technology(KIT), Germany)

2:05 pm – 2:25 pm:

A Study of Performance Optimization Techniques of Digital Integrated Circuit Test Generation System

*CHAO Zhiteng (Institute of Computing Technology, Chinese Academy of Sciences)

Session 2 (ITC-Asia) @Room 802: Test Challenges in 3D ICs and ATE

Chair: Tsuyoshi Iwagaki (Hiroshima City University)

1:00 pm – 1:25 pm:

[RS2-1] Descriptive Language For 3D IC Die-to-Die Interconnect Repair For IEEE P3405 Standard

Ashish Reddy Bommana, *Anshuman Chandra, Moiz Khan (Siemens EDA)

1:25 pm – 1:50 pm:

[RS2-2] A High-Precision Pre-Bond TSV Delay-Fault Detection Technique Using Digitally Controlled Delay Lines

*Zhongyuan Liang (School of Microelectronics Hefei University of Technology), Huaguo Liang (Hefei University of Technology), Weikun Chen (School of Computer and Information Hefei University of Technology), Xianrui Dou (School of Microelectronics Hefei University of Technology)

1:50 pm – 2:15 pm:

[RS2-3] A mm-Wave Frontend Circuit with High Accuracy Power Levels for ATE to Test 76- to 81- GHz Radar IC

*Norio Kobayashi (Advantest Corporation), Minoru Iida, Masayuki Nakamura, Hideki Shirasu (ADVANTEST CORPORATION)

2:15 pm – 2:40 pm:

[RS2-4] A Kelvin Connection-Based Approach Using an Internal DFT Technique To Compensate Resistance Variability In Semiconductor Testing

*Rinika Paul (ATE Test Engineer, Infineon Technologies, India)

Dec. 17 (Wednesday) 3:00 pm – 5:05 pm

Session 3 (ATS) @Room 101: AI for Test and Test for AI

Chair: Chih-Tsun Huang (National Tsing Hua University)

3:00 pm – 3:25 pm:

[RS3-1] AssertGen: Enhancement of LLM-aided Assertion Generation through Cross-Layer Signal Bridging

*Hongqin Lyu, Yonghao Wang (Institute of Computing Technology, Chinese Academy of Sciences), Yunlin Du (University of Newcastle), Mingyu Shi (NANJING UNIVERSITY SCHOOL OF INTEGRATED CIRCUITS), Zhiteng Chao, Wenxing Li, Tiancheng Wang, Huawei Li (Institute of Computing Technology, Chinese Academy of Sciences)

3:25 pm – 3:50 pm:

[RS3-2] Exploring the Limits of LLMs for System-Level Test Program Generation: Can LLaMas Outrun Darwin?

*Denis Schwachhofer, Steffen Becker (University of Stuttgart), Stefan Wagner (Technical University of Munich), Matthias Sauer (Advantest Europe GmbH), Ilia Polian (University of Stuttgart)

3:50 pm – 4:15 pm:

[RS3-3] Transformer-Based Architecture for Fault Propagation Modeling in Transient Fault Analysis

Chia-Ying Lin (Dept. Electrical Engineering, National Tsing Hua University), *Jing-Jia Liou (Dept. Electrical Engineering/National Tsing Hua University), Harry H. Chen (MediaTek Inc.)

4:15 pm – 4:40 pm:

[RS3-4] Testing of Passive Memristive Crossbars in AI Hardware Accelerators

*Shanmukha Mangadahalli Siddaramu (karlsruhe institute of technology), Mahta Mayahinia, Surendra Hemaram (Karlsruhe Institute of Technology (KIT)), Sule Ozev (Arizona State University), Mehdi Tahoori (Karlsruhe Institute of Technology)

Session 4 (ATS) @Room 802: Chiplet and Interconnect Reliability

Chair: Krishnendu Chakrabarty (Arizona State University)

3:00 pm – 3:25 pm:

[RS4-1] The Low-Latency UCIe-Compliant Spiral Layouts of TSV Arrays Against the Clustered Faults

*Bowen Tan, Xiaole Cui, Zhaohong Lin (Peking University Shenzhen Graduate School)

3:25 pm – 3:50 pm:

[RS4-2] LLM-Design Platform for Thermal-Failure-Aware 3D Chiplet Layout via Iterative Parameter Analysis

*Tai Song (Anhui University), Senling Wang (Dept. of Computer Science, Faculty of Engineering, Ehime University), Xiaoqing Wen (Graduate School of Computer Science and Systems Engineering, Kyushu Institute of Technology)

3:50 pm – 4:15 pm:

[RS4-3] Software-Defined Secure Island for Testing Chiplet Systems

*Hisashi Okamoto (Ehime University), Senling Wang (Dept. of Computer Science, Faculty of Engineering, Ehime University), Hiroshi Kai, Hiroshi Takahashi, Yoshinobu Higami (Ehime University), Hiroyuki Yotsuyanagi (Tokushima University), Tianming Ni (Anhui Polytechnic University), Tai Song (Anhui University), Xiaoqing Wen (Graduate School of Computer Science and Systems Engineering, Kyushu Institute of Technology)

4:15 pm – 4:40 pm:

[RS4-4] Fault-Aware Repair Scheme for Inter-Die Interconnects of Chiplet-Based Chips

*Yi-Chun Huang, Jin Fu Li, Hong-Siang Fu (National Central University), Yung-Ping Lee (Industrial Technology Research Institute)

4:40 pm – 5:05 pm:

[RS4-5] Chiplet Interconnect Repair for Clustered Defects with Minimal Propagation Delay

*Po-Yao Chuang, Erik Jan Marinissen (imec)

Session 5 (ITC-Asia) @Room 702: Timing Monitoring and Optimization

Chair: Shi-Yu Huang (National Tsing Hua University)

3:00 pm – 3:25 pm:

[RS5-1] Monitor-Like Efficiency with Detector-Level Accuracy: Frontier-Aligned Timing Monitor for AI Accelerators

*Wei-Ji Chao, Tsung-Chun Chen (Department of Electrical Engineering, National Sun Yat-sen University), Chu-Cheng Chen (Institute of Integrated Circuit Design, National Sun Yat-sen University), Tong-Yu Hsieh (National San Yat-san University)

3:25 pm – 3:50 pm:

[RS5-2] A Fast Nonlinear Trimming Method Driven by Performance Deviation

*Yangxinzi Zhou, Wenfa Zhan, Jiangyun Zheng, Xueyuan Cai, Shiyu Zhao (Anqing Normal University)

3:50 pm – 4:15 pm:

[RS5-3] Automatic IR-Informed Timing and Timing-Aware IR Optimization

Po-Chieh Yen, Wei-Shen Wang, *Shao-Yu Wu, Bing-Chen Li, James Chien-Mo Li (National Taiwan University), Norman Chang, Ying-Shiun Li, Lang Lin, Akhilesh Kumar (Ansys Inc.)

Dec. 17 (Wednesday) 6:30 pm – 9:00 pm

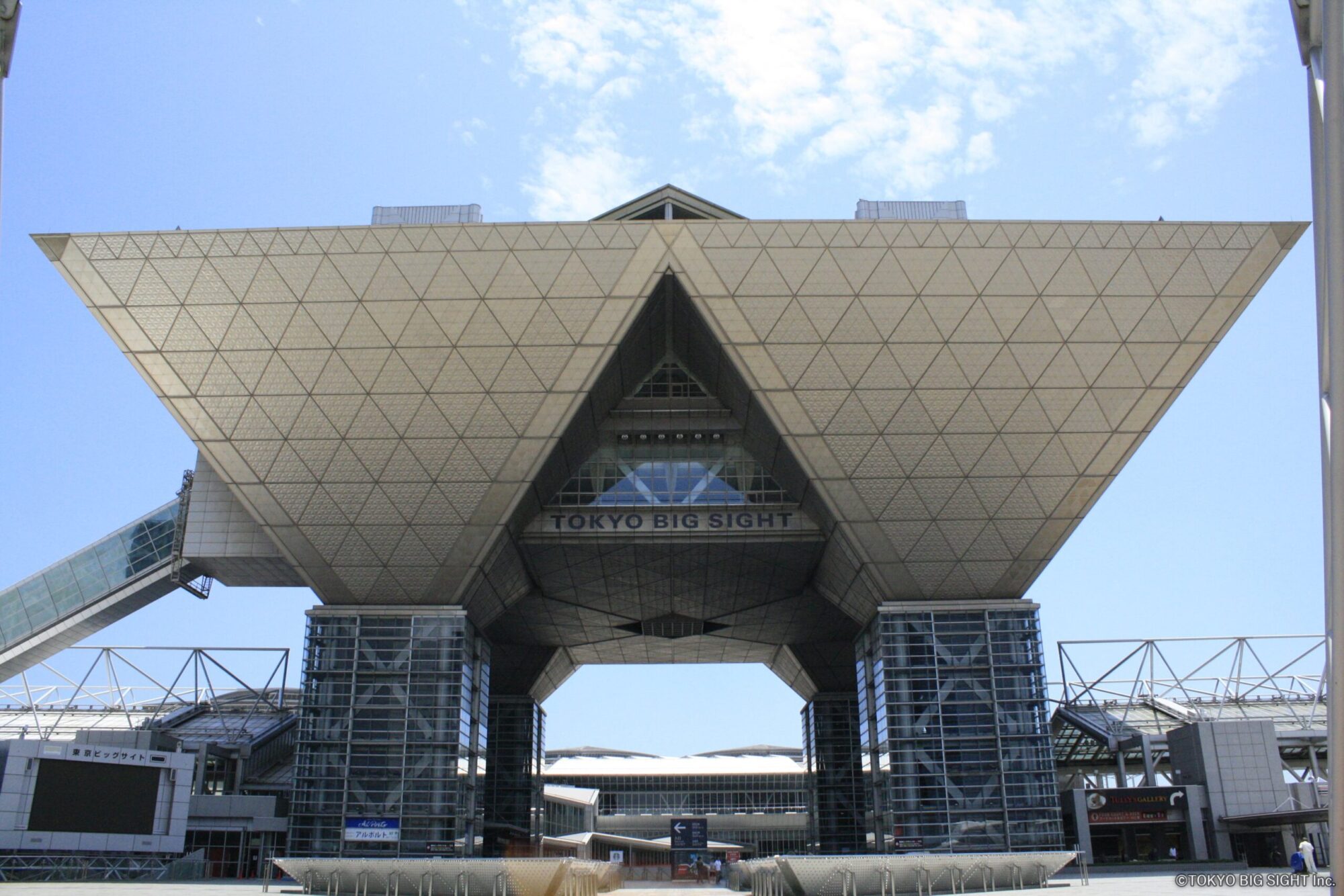

Banquet @Hilton Tokyo Odaiba

Dec. 18 (Thursday) 9:00 am – 10:40 am

Keynote 2 / Invited Talk 2 @Room 701+702

Chair: Hiroyuki Yotsuyanagi (Tokushima University)

9:00 am – 9:50 am:

[K2] Software-Based Self-Test with Formal Methods for RISC-V Ecosystems

*Bernd Becker (University of Freiburg)

9:50 am – 10:40 am:

[I2] Next-Generation SoC Design “Chiplet 2.5D/3D Technology” and Beyond

*Kazuyuki Irie (TSMC Group, GUC Japan)

Dec. 18 (Thursday) 11:00 am – 12:40 pm

Session 6 (ITC-Asia) @Room 701+702: Emerging Paradigms in Test, Security, and Reliability

Chair: Jin-Fu Li (National Central University)

11:00 am – 11:25 am:

[RS6-1] FALCO-WAFER : Feature-Aware Lightweight Contextual Detector for Wafer Defect Detection

*Haotian Zhang, Shurong Cao, Ningmu Zou (School of Integrated Circuits, Nanjing University, Suzhou, China.)

11:25 am – 11:50 am:

[RS6-2] Design for Testability for VLSI Circuits with A Large Number of Unknown Test Response Sources

*Dong Xiang, Wenfei Wang (Tsinghua University)

11:50 am – 12:15 pm:

[RS6-3] Fault-Detecting Randomized Benchmarking for Testing Quantum Processors

Cynthia Kuan, Cheng-Yun Hsieh, *Shan-Chi Shih, James Chien-Mo Li (National Taiwan University)

12:15 pm – 12:40 pm:

[RS6-4] Collide & Conquer: Side-channel Attack on Hyper-dimensional Computing (HDC) Accelerators

Brojogopal Sapui (Kalrsurhe Institute of Technology, Germany), *Mahboobe Sadeghipour Roudsari, Mehdi Tahoori (Karlsruhe Institute of Technology)

Session 7 (ATS) @Room 802: RF Calibration and ADC Test

Chair: Haruo Kobayashi (Gunma University)

11:00 am – 11:25 am:

[RS7-1] Multi-Agent Reinforcement Learning for Performance Calibration and Optimization of Integrated mmW Power Amplifiers

*Valentin Coppola, Florent Cilici, Sylvain Bourdel, Estelle Lauga-Larroze, Salvador Mir, Florence Podevin, Manuel Barragan (TIMA)

11:25 am – 11:50 am:

[RS7-2] Ultra-Fine Frequency Offset Synthesis Technique Based on Cascaded Phase Interpolators

Cao Wang (Shanghai Jiao Tong University), Shengbo Liu, Yindong Xiao (University of Electronics Science and Technology of China), Xiaochun Li (Shanghai Jiao Tong University), *David Keezer (Eastern Institute of Technology, Ningbo)

11:50 am – 12:15 pm:

[RS7-3] TDR-Based S-Parameter Estimation of Signal Path to DUT Utilizing Built-In Driver and Comparator of ATE

*Kazuki Shirahata, Masahiro Ishida (ADVANTEST Corp.), Koji Asami, Toru Nakura, Akio Higo, Tetsuya Iizuka (The University of Tokyo)

12:15 pm – 12:40 pm:

[RS7-4] Advanced Strategies for Uncertainty‑Guided Live Measurement Sequencing in Fast, Robust SAR ADC Linearity Testing

*Thorben Schey (University of Stuttgart), Khaled Karoonlatifi (Advantest Europe GmbH), Michael Weyrich, Andrey Morozov (University of Stuttgart)

Dec. 18 (Thursday) 1:30 pm – 3:10 pm

Special Session @Room 701+702: “6 Years of Graduate School Intelligent Methods Test and Reliability”

Organizer: Ilia Polian (University of Stuttgart, member of GS-IMTR Board of Directors)

1:40 pm – 1:50 pm:

Introduction into Graduate School Intelligent Methods Test and Reliability

*Ilia Polian (University of Stuttgart, member of GS-IMTR Board of Directors)

1:50 pm – 2:20 pm:

Beyond Today: Shaping the Future of the Semiconductor Industry

*Kotaro Hasegawa (Senior Vice President Advantest Japan)

2:20 pm – 2:32 pm:

Intelligent Sensing and On-Chip Learning for Silicon Lifecycle Management

*Tim Strobel (University of Stuttgart, PhD student)

2:32 pm – 2:44 pm:

Automated Extraction of Interpretable Variable Expressions for Semiconductor Test Data Analysis

*Yang Yang (University of Stuttgart, PhD student)

2:44 pm – 2:56 pm:

Analytics Driven Intelligent Device Tester Calibration

*Anand Venkatachalam (University of Stuttgart, PhD student)

2:56 pm – 3:08 pm:

Adaptive Real-Time Decision Making in Mixed-Signal Testing

*Thorben Schey (University of Stuttgart, PhD student)

Session 8 (ITC-Asia) @Room 802: ATPG and Diagnosis

Chair: Jing-Jia Liou (National Tsing Hua University)

1:30 pm – 1:55 pm:

[RS8-1] Improving Effect-Cause Diagnosis Performance with Minimal Memory Overhead on Asymmetric Partition Trees (APT)

*Wu-Tung Cheng, Szczepan Urban, Manish Sharma, Jakub Janicki (Siemens EDA)

1:55 pm – 2:20 pm:

[RS8-2] Exploiting weak detections for optimizing pattern generation in Defect-Oriented Cell-Aware ATPG

*Alessandro Ciullo, Stephan Eggersglüß, Daniel Tille, Andreas Glowatz (Siemens EDA), Giusy Iaria, Paolo Bernardi (Politecnico di Torino)

2:20 pm – 2:45 pm:

[RS8-3] Improving ATPG through Abort-Driven Dynamic Learning (ADDLe)

*Peter Wohl, John Waicukauski, Jonathon Colburn, Yasunari Kanzawa (Synopsys)

2:45 pm – 3:10 pm:

[RS8-4] Test Point Insertion for an Approximate Multiplier Using Enhanced Static Segment Method to Reduce Test Patterns and Overdetection

*Takuya Kishimoto, Hiroyuki Yotsuyanagi (Tokushima University)

Dec. 18 (Thursday) 3:25 pm – 5:05 pm

Industry Session @Room 701+702

Chair: Kazumi Hatayama (EVALUTO)

3:25 pm – 3:50 pm:

[IS-1] Silicon Lifecycle Management: From Design to In-Field Reliability

*Wu Yang (Siemens EDA)

3:50 pm – 4:15 pm:

[IS-2] Synopsys Scalable E2E Test Solution with AI Driven Optimization

Yuya Suzuki, Shamitha Rao, and *Sri Ganta (Synopsys)

4:15 pm – 4:40 pm:

[IS-3] Case Studies of Test Solutions in 3D-IC and Efforts to Reduce Test Time

*Shuji Hamada (Socionext)

4:40 pm – 5:05 pm:

[IS-4] Beyond AI: Securing the Future of IC Design

*Marc X. Makkes (Fortaegis Technologies)

Session 9 (ATS) @Room 802: Physical Unclonable Function, Verification and Radiation-hardening

Chair: Senling Wang (Ehime University)

3:25 pm – 3:50 pm:

[RS9-1] Radiation-Resistant ZnO Thin-Film Transistor Voltage Reference

Na Bai, *Guocheng Ge (Anhui University), Aibin Yan (Hefei University of Technology), Xiaoqing Wen (Kyushu Institute of Technology)

3:50 pm – 4:15 pm:

[RS9-2] Veritas-PUF: A Countermeasure against X-Ray Tampering and Side Channel Attacks

*Nasr-Eddine Ouldei Tebina (TIMA/Fortaegis Technologies), Luc Salvo (SIMAP/Grenoble INP), Marc Xander Makkes (Fortaegis Technologies), Nacer-Eddine Zergainoh (TIMA), Paolo Maistri (TIMA/CNRS)

4:15 pm – 4:40 pm:

[RS9-3] Improving RO-PUFs on FPGAs: A Filtering Approach for Improved Reliability and Entropy

*Vasilii Kulagin, Giorgio Di Natale (TIMA), Elena-Ioana Vatajelu (TIMA, CNRS)

4:40 pm – 5:05 pm:

[RS9-4] EMBER: A Cycle-based Framework for Early-Stage Reliability Assessment in Parametric RTL Designs

*Alessandro Veronesi, Leticia Maria Bolzani Pöhls (IHP-microelectronics), Michele Favalli (University of Ferrara), Milos Krstic (IHP-microelectronics), Davide Bertozzi (University of Manchester)

Dec. 19 (Friday) 9:00 am – 10:40 am

Session 10 (ATS) @Room 701: Memory Testing and Optimization

Chair: Satoshi Ohtake (Oita University)

9:00 am – 9:25 am:

[RS10-1] Dynamic Step-Size Single-Write Pattern Trimming for STT-MRAM Reference Resistance Optimization

*Chenxi Liu (Zhejiang University), Yaxing Zhou (Zhejiang Hikstor Technology Co., Ltd.), Pingyang Huang (Zhejiang University), Shikun He (Zhejiang Hikstor Technology Co., Ltd.), Zhiyuan Cheng (Zhejiang University)

9:25 am – 9:50 am:

[RS10-2] Two-Step Transition Zeroization Techniques for MLC STT-MRAM

Shyue-Kung Lu, *Tzu-En Huang (National Taiwan University of Science and Technology), Kohei Miyase (Kyushu Institute of Technology)

9:50 am – 10:15 am:

[RS10-3] Streamlining MBIST Footprint : A Strategic Approach through Memory Centric Clustering and Controller Placement

Manya Gupta, *Somya Gupta, Arshad Qureshi, Vishal Diwan (Texas Instruments)

10:15 am – 10:40 am:

[RS10-4] March-CIM: An MBIST-guided Modified March Test for SRAM-based Computation-in-Memory

*Sina Bakhtavari Mamaghani (Karlsruhe Institute of Technology), Jongsin Yun, Martin Keim (Siemens EDA), Mehdi Tahoori (Karlsruhe Institute of Technology)

Session 11 (ITC-Asia) @Room 702: Fault Tolerance and Reliability

Chair: Yousuke Miyake (PRIVATECH Inc.)

9:00 am – 9:25 am:

[RS11-1] A Speed Learning Scheme To Mitigate The Silent Data Corruption in a Multi-Core Design

Yun-Chieh Wang, Chun-Teng Chao (NTHU), *Shi-Yu Huang (NTHU, STPI/NIAR), Robert Chen (Taiwan Electronic System Design Automation)

9:25 am – 9:50 am:

[RS11-2] Fault Injection and Tolerance Analysis of Battery Management Systems Using SystemC-AMS

Hao-Yang Chi, *Chih-Tsun Huang, Jing-Jia Liou (Dept. Electrical Engineering/National Tsing Hua University), Harry Chen (MediaTek)

9:50 am – 10:15 am:

[RS11-3] Analysis and Improvement of Parallel Implementation of Linear FSMs for High-Speed Stochastic Computing

*Hideyuki Ichihara, Kota Okahara, Tomoo Inoue (Hiroshima City University)

10:15 am – 10:40 am:

[RS11-4] Adaptive Fault Resilience for Early-Exit DNNs

*Rama Mounika Kodamanchili, Natalia Cherezova (Tallinn University of Technology), Mahdi Taheri (Brandenburg Technical University, Cottbus, Germany), Maksim Jenihhin (Tallinn University of Technology)

ETT workshop (Session 1) @Room 802: Fault Tolerant Design and Testability Analysis

Chair: Hiroyuki Yotsuyanagi (Tokushima University)

9:00 am – 9:05 am:

Opening (ETT workshop)

9:05 am – 9:25 am:

[ETT1-1] REQAP: Resilient Weight Packing and Quantization for DNN Acceleration

*Mahdi Taheri1,2, Samira Nazari3, Ali Azarpeyvand2,3, Mohsen Afsharchi3, Christian Herglotz1, and Maksim Jenihhin2 (1Brandenburg Technical University, Cottbus, Germany; 2Tallinn University of Technology, Tallinn, Estonia; 3University of Zanjan, Zanjan, Iran)

9:25 am – 9:45 am:

[ETT1-2] LLM–Driven Testability Analysis for Gate-Level Circuits

*Akitaka Ide, Senling Wang, Hiroshi Kai, Yoshinobu Higami, Hiroshi Takahashi (Ehime University, Japan)

9:45 am – 10:05 am:

[ETT1-3] RTL Testability for RTL Datapath Based on Network Centrality

*Saki Sugiyama, Ken’ichi Yamaguchi, Hiroshi Iwata (National Institute of Technology, Nara College, Japan)

10:05 am – 10:25 am:

[ETT1-4] A Design for Diagnosability Method Based on Don’t Care Filling of Control Signals at Register Transfer Level

*Toshinori Hosokawa, Yui Otsuka(Nihon University, Japan), Koji Yamazaki(Meiji University, Japan), Masayoshi Yoshimura(Kyoto Sangyo University, Japan) and Masayuki Arai(Nihon University, Japan)

Dec. 19 (Friday) 10:55 am – 12:35 pm

Session 12 (ATS) @Room 701: Fault Tolerance and Reliability

Chair: Michiko Inoue (Nara Institute of Science and Technology)

10:55 am – 11:20 am:

[RS12-1] How Long Can They Learn? A Methodology to Assess Endurance in Analog Memristive Synapses during On-line Training

Alexandra Koroleva (TIMA Laboratory), Salah Daddinounou (TIMA – INPG), Monica Burriel (LMGP – CNRS), *Elena Ioana Vatajelu (TIMA – CNRS)

11:20 am – 11:45 am:

[RS12-2] Reliability Assessment of Early Exit Deep Convolutional Neural Networks

*Georgios Konstantinidis, Maria K. Michael, Theocharis Theocharides (University of Cyprus and KIOS Research and Innovation Center of Excellence)

11:45 am – 12:10 pm:

[RS12-3] Breaking the One-Shot Barrier: Progressive Error Detection in FSM via Key-Driven Corruption

Leon Li, *Alex Orailoglu (University of California, San Diego)

12:10 pm – 12:35 pm:

[RS12-4] Fault-Tolerant and Low-Latency Stochastic Neural Networks via Adaptive Bitstream Precision

*Roshwin Sengupta (University of Stuttgart), John P. Hayes (University of Michigan), Ilia Polian (University of Stuttgart)

ETT workshop (Session 2) @Room 802: Test and DFT Techniques for RF, 3D, and Asynchronous Circuits

Chair: Hideyuki Ichihara (Hiroshima City University)

10:55 am – 11:15 am:

[ETT2-1] A 30 MHz – 260 GHz TestBed for Design and Characterization of Broadband RF ICs and Systems Using NI’s VST Platform

Clint Sweeney, *Donald Y.C. Lie, Felipe Silva(Texas Tech U.), Amr Haj-Omar(Morgan State U.), Jerry Lopez(Texas Tech U. and NoiseFigure Research)

11:15 am – 11:35 am:

[ETT2-2] A simple full scan design using scan C flip-flop for asynchronous circuit

*Hiroaki Shimaoka, Hiroshi Iwata, Ken’ichi Yamaguchi (National Institute of Technology, Nara College, Japan)

11:35 am – 11:55 am:

[ETT2-3] Parallel BISR Chain Loading for Fast Repair

*Liutao Lin, Xinchen Xie, Junna Zhong (Siemens Digital Industries Software)

11:55 am – 12:15 pm:

[ETT2-4] A Boundary Scan Design with Interconnect Delay Testing and Region-based Repair for TSVs

*Haruhisa Tsuruoka, Hiroyuki Yotsuyanagi(Tokushima University, Japan), Masaki Hashizume(The Open University of Japan, Japan), Senling Wang, Yoshinobu Higami, Hiroshi Kai, Hiroshi Takahashi(Ehime University, Japan), Tianming Ni(Anhui Polytechnic University, China) and Xiaoqing Wen(Kyushu Institute of Technology, Japan)

Dec. 19 (Friday) pm 1:00 pm – 2:35 pm

AI-TREATS Workshop (Session 1) @Room 802

1:00 pm – 1:05 pm:

Opening remarks (AI-TREATS Workshop)

Fei Su (Tsinghua University, Program Co-Chair)

1:05 pm – 1:35 pm:

[Invited Talk 1] Built-in Fault Tolerance for Deep Learning Systems

Huawei Li (Chinese Academy of Sciences)

1:35 pm – 2:05 pm:

[Invited Talk 2] Fault-Tolerant ReRAM-based Crossbars for AI Accelerators

Krishnendu Chakrabarty (Arizona State University)

2:05 pm – 2:35 pm:

[Invited Talk 3] Test Compression, Compact Test Pattern Generation for AI Chip Based on Software-Defined Linear Feedback Shift-Register

Dong Xiang (Tsinghua University)

Dec. 19 (Friday) pm 2:50 pm – 5:00 pm

AI-TREATS Workshop (Session 2) @Room 802

2:50 pm – 3:20 pm:

[Contributed Talk 1] Feasibility of Temporal Processing on MRP

*Kenta Sasagawa, Senling Wang and Hiroshi Takahashi (Ehime University)

3:20 pm – 3:50 pm:

[Contributed Talk 2] Structural assessment of System-Level Test programs for AI accelerators embedded into Automotive SoCs

*Giusy Iaria (Politecnico di Torino), Paolo Bernardi (University of Padova), Claudia Bertani and Vincenzo Tancorre (STMicroelectronics)

3:50 pm – 4:20 pm:

[Contributed Talk 3] Stealing AI Model Weights Through Covert Communication Channels

Valentin Barbaza, *Alan Rodrigo Diaz-Rizo, Hassan Aboushady, Spyridon Raptis and Haralampos-G. Stratigopoulos (Sorbonne University)

4:20 pm – 4:50 pm:

[Contributed Talk 4] SAFPA: Reliability Assessment Method for DNN Inference on Systolic Arrays Based on Fault Propagation Analysis

Natalia Cherezova, Artur Jutman and *Maksim Jenihhin (Tallinn University of Technology)

4:50 pm – 5:00 pm:

Closing remarks (AI-TREATS Workshop)

Fei Su (Tsinghua University, Program Co-Chair)